Categories:

LLVM 指令的一生 (Life of an instruction in LLVM)

推荐阅读

- Life of an instruction in LLVM - Eli Bendersky’s website (thegreenplace.net)

- 【llvm-dev】 Writing a Pass in LLVM MC (Machine Code) level to Analyze Assembly Code

- Chapter “Understanding the machine code framework” - “Getting Started with LLVM Core Libraries by Bruno and Rafael

- Building an LLVM backend.pdf - Fraser and Pierre-Andre

- Lele’s Memo: The

MCLayer in LLVM (cnlelema.github.io) - ushitora-anqou/write-your-llvm-backend: 手を動かせばできるLLVMバックエンド チュートリアル(WIP) (github.com)

Life of an Instruction in LLVM

- Life of an instruction in LLVM - Eli Bendersky’s website (thegreenplace.net)

- ushitora-anqou/write-your-llvm-backend: 手を動かせばできるLLVMバックエンド チュートリアル(WIP) (github.com)

- 跟随一条指令来看LLVM的基本结构_P2Tree的博客-CSDN博客

- compiler/life-of-instruction-LLVM.pdf at main · randoruf/compiler (github.com)

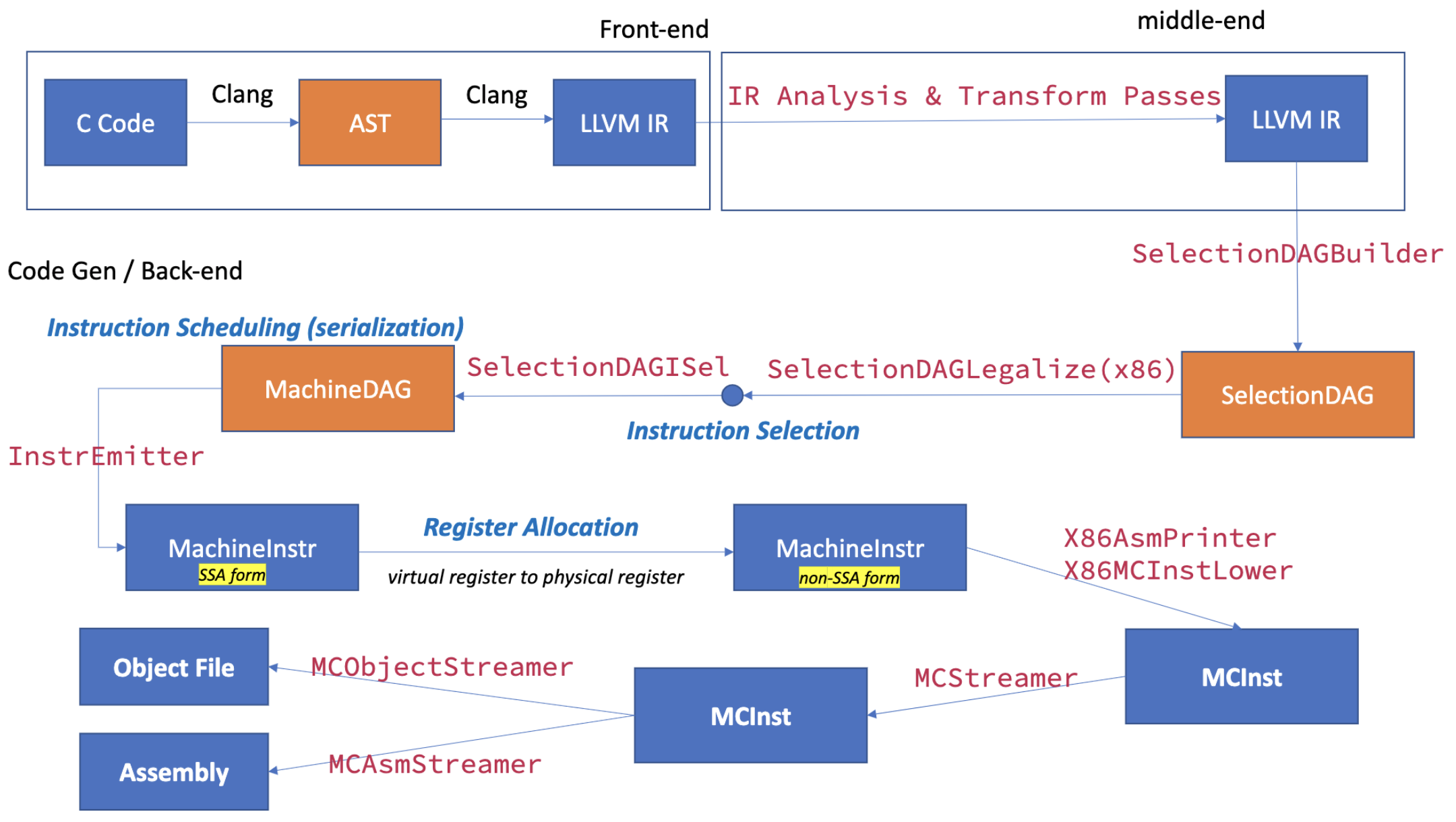

LLVMバックエンドの流れ

CAHP* はオーバーライドできるメンバ関数を表す。

LLVM IR code

|

|

v

SelectionDAG (SDNode); CAHPで扱えない型・操作を含む (not legal)。

|

| <-- CAHPTargetLowering::CAHPTargetLowering

| <-- CAHPTargetLowering::Lower*

v

SelectionDAG (SDNode); CAHPで扱える型・操作のみを含む (legal)。

|

| <-- CAHPDAGToDAGISel, CAHPInstrInfo

v

SelectionDAG (MachineSDNode); ノードの命令は全てCAHPのもの。

|

| <-- CAHPInstrInfo; 命令スケジューリング

v

LLVM MIR (MachineInstr); スケジューリングされた命令列

| (以下の流れは TargetPassConfig::addMachinePasses に記述されている)

|

| <-- CAHPTargetLowering::EmitInstrWithCustomInserter;

| usesCustomInserter フラグが立っている ある MachineInstr の代わりに

| 複数の MachineInstr を挿入したり MachineBasicBlock を追加したりする。

|

| <-- SSA上での最適化

|

| <-- レジスタ割り付け

v

LLVM MIR (MachineInstr); 物理レジスタのみを含む命令列(仮想レジスタを含まない)

|

| <-- CAHPInstrInfo::expandPostRAPseudo

|

| <-- CAHPFrameLowering::processFunctionBeforeFrameFinalized

|

| <-- スタックサイズの確定

|

| <-- CAHPFrameLowering::emitPrologue; 関数プロローグの挿入

| <-- CAHPFrameLowering::emitEpilogue; 関数エピローグの挿入

| <-- CAHPRegisterInfo::eliminateFrameIndex; frame indexの消去

|

| <-- llvm::scavengeFrameVirtualRegs;

| frame lowering中に必要になった仮想レジスタをscavengeする

v

LLVM MIR (MachineInstr); frame index が削除された命令列

|

| <-- CAHPPassConfig::addPreEmitPass

| <-- CAHPPassConfig::addPreEmitPass2

|

|

| <-- CAHPAsmPrinter

| <-- PseudoInstExpansion により指定された擬似命令展開の実行

v

MC (MCInst); アセンブリと等価な中間表現

LLVM MIRについては[46]に詳しい。 各フェーズでの MachineInstr をデバッグ出力させる場合は llc に -print-machineinstrs を 渡せば良い。